# THE MELITIERA SE

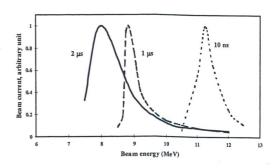

# Proceedings of the 2<sup>nd</sup> SIRAD Workshop

INFN Laboratori Nazionali di Legnaro Legnaro, Padova, Italy April 1-2, 2004

Editor

A. Candelori

INFN Sezione di Padova

## PROCEEDINGS OF THE 2<sup>ND</sup> SIRAD WORKSHOP

INFN Laboratori Nazionali di Legnaro Legnaro, Padova, Italy April 1-2, 2004

#### **EDITOR**

Dr. Andrea Candelori

#### **ORGANIZING COMMITTEE**

Prof. Dario Bisello

Prof. Giovanni Busatto

Dr. Andrea Candelori

Prof. Alessandro Paccagnella

Prof. Jeff Wyss

#### INTRODUCTION

The 2<sup>nd</sup> SIRAD Workshop was dedicated to the study of radiation effects (bulk damage, total dose and single events) in silicon detectors, electronic devices and systems for Space and High-Energy Physics applications. The purpose of the Workshop was to continue and increase the stimulating interaction within Universities, Institutes, Industries and Companies operating in the Italian Radiation Effect Community and to be a starting point for new collaborations with Italian and foreign Institutions.

The 2<sup>nd</sup> SIRAD Workshop was held in the Main Conference Room (Aula Villi) of the INFN National Laboratory of Legnaro, April 1-2, 2004: 52 scientists and researchers from different Italian Universities (Padova, Cassino, Torino, Perugia, Pavia), Research Institutes (INFN Section of Padova, Firenze, Bari, Trieste, Perugia, INFN National Laboratory of Legnaro, ENEA, CNR-IASF, CNR-ISOF, CARSO, ITC-irst), Industries (Alenia Spazio, Aurelia Microelettronica, Galileo Avionica, ST Microelectronics, Tecnomare) and Foreign Institutions (CERN, ESA, Helsinki Institute for Particle Physics) participated to the Workshop.

The Workshop highlighted the importance and the interest in Italy and at an international level of the research activities concerning radiation damage in silicon detectors, electronic devices and systems for High Energy Physics and Space applications.

The Workshop was divided in four main sessions:

- 1) Silicon Detectors;

- 2) Electronics for Space;

- 3) Electronics for High Energy Physics and Astrophysics Experiments;

- 4) Facilities for Radiation Testing.

The presentations of the Workshop are online available:

http://sirad.pd.infn.it/sirad/WEB/Index.htm.

Finally it was decided to organize the "Italian Group for Radiation Effect Studies, Testing and Applications (IGRESTA)" open to Universities, Research Institutes, Industries and Companies, which are interested to participate. The purpose of IGRESTA is to develop/maintain an Italian coordination of the groups which perform research and/or have interest for studying/developing electronics and sensors for High Energy Physics and Astrophysics experiments, Space applications and/or technological applications of radiation (for instance nuclear techniques for localization of explosive materials, material page online The IGRESTA WEB is sterilization, and SO on). (http://www.igresta.it) for more information.

#### THE WORKSHOP WAS ORGANIZED WITH THE SUPPORT OF

- -INFN Laboratori Nazionali di Legnaro;

- -INFN Sezione di Padova;

- -Dipartimento di Ingegneria dell'Informazione, Università degli Studi di Padova;

- -Dipartimento di Fisica, Università degli Studi di Padova;

- -DIMSAT and DAEIMI, Università degli Studi di Cassino.

#### **ACKNOWLEDGEMENTS**

We thank Dr. Graziano Fortuna, Director of INFN Laboratori Nazionali di Legnaro, and Prof. Gianni Zumerle, Director of INFN Sezione di Padova, who supported the organization of the Workshop; Dr. D. R. Napoli for his suggestions to improve the publication.

### **INDEX**

#### SESSION I: RADIATION HARDENING OF SILICON DETECTORS

| -"Status of the development of ultra radiation-hard semiconductor detectors for very high luminosity colliders", $M.\ Bruzzi$                                                                                                                                                                                                                | <u>:</u> |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| -"RADIATION DAMAGE MEASUREMENTS FOR THE ALICE PIXEL DETECTORS", M. Cinausero, E. Fioretto, G. Prete, L. Vannucci, F. Antinori, R. Dima, D. Fabris, M. Lunardon, S. Martini, S. Moretto, A. Pepato, F. Scarlassara, G. Segato, F. Soramel, R. Turrisi, G. Viesti, A. Candelori, D. Bisello, A. Kaminski, D. Pantano, P. Riedler, G. Stefanini | 2        |

| -"DEVELOPMENT OF CZOCHRALSKI SILICON PARTICLE DETECTORS",<br>J. Härkönen, P. Luukka, E. Tuovinen, E. Tuominen                                                                                                                                                                                                                                | 11       |

| -"Development of a fabrication technology for PIN diodes on thinned silicon substrate", S. Ronchin, M. Boscardin, GF. Dalla Betta, P. Gregori, V. Guarnieri, C. Piemonte, N. Zorzi                                                                                                                                                           | 14       |

| -"RADIATION HARDNESS OF DIFFERENT SILICON MATERIALS AFTER HIGH-ENERGY ELECTRON IRRADIATION",                                                                                                                                                                                                                                                 |          |

| S. Dittongo, L. Bosisio, M. Ciacchi, D. Contarato, G. D'Auria, E. Fretwurst, G. Lindström                                                                                                                                                                                                                                                    | 17       |

| SESSION II: RADIATION EFFECTS IN ELECTRONICS FOR SPACE                                                                                                                                                                                                                                                                                       |          |

| -"Ultra-thin gate oxide radiation induced wear-out after heavy ion irradiation: a statistical model", S. Cimino, A. Cester, E. Mirando, A. Paccagnalla, G. Ghidini, A. Candelori                                                                                                                                                             | 23       |

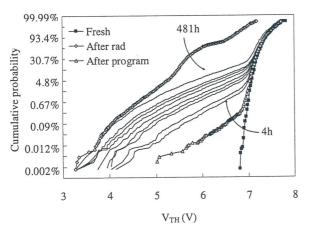

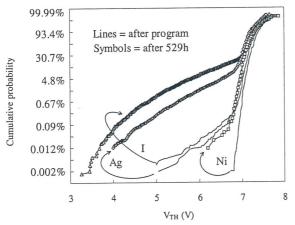

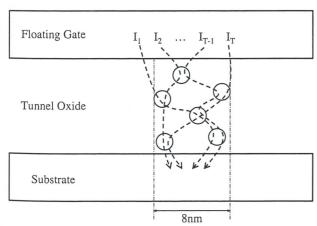

| -"Data retention of irradiated Floating Gate memories",<br>G. Cellere, L. Larcher, A. Paccagnella, A. Modelli, A. Candelori                                                                                                                                                                                                                  | 27       |

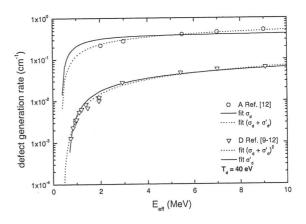

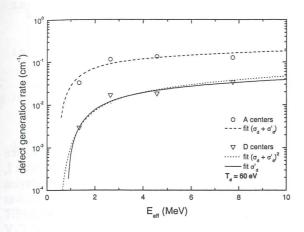

| -"Radiation induced defects in bipolar power transistors: influence of radiation energy",<br>M. Lavalle, U. Corda, P. G. Fuochi, G. Lulli, E. Gorbia                                                                                                                                                                                         | 31       |

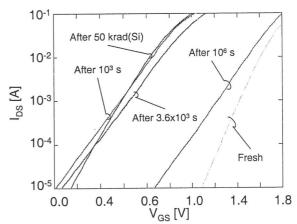

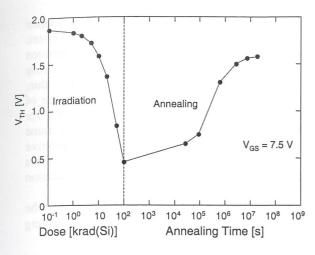

| "TOTAL DOSE EFFECTS IN POWER MOSFETS", L. Bandiera, A. Paccagnella, S. Cimino and S. Lora                                                                                                                                                                                                                                                    | 34       |

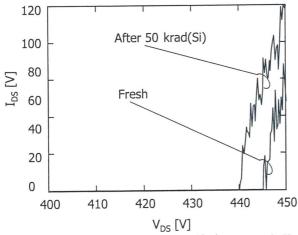

| -"Experimental study on the reliability of low blocking voltage power VDMOSFET during heavy ion exposure",                                                                                                                                                                                                                                   |          |

| F. Velardi, F. Iannuzzo, G. Busatto, J. Wyss, A. Sanseverino, G. Currò, A. Cascio, F. Frisina                                                                                                                                                                                                                                                | 37       |

| -"RADIATION SUSCEPTIBILITY TRIALS ON COTS CAMERAS FOR THE INTERNATIONAL SPACE STATION", M. Zampato, R. Finotello, R. Ferrario, A. Viareggio, S. Losito                                                                                                                                                                                       | 39       |

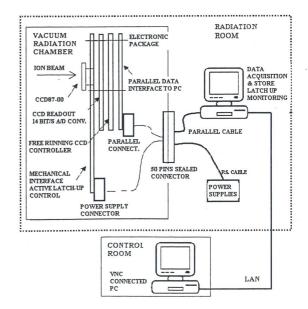

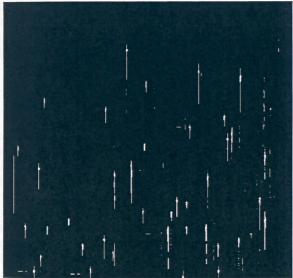

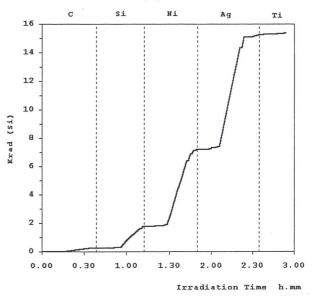

| -"HEAVY ION TEST ON E2V CCD87 FOR THE AMS-02 EXPERIMENT ON THE INTERNATIONAL SPACE STATION",                                                                                                                                                                                                                                                 | 4:       |

| M. Albi, A. Bucconi, F. Turchet                                                                                                                                                                                                                                                                                                              | 43       |

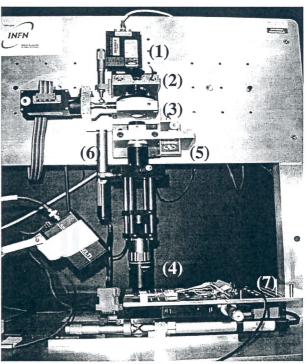

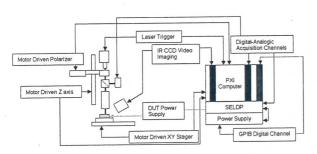

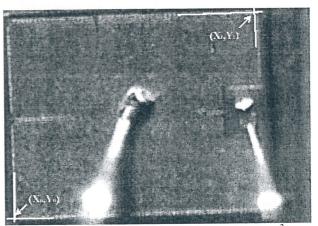

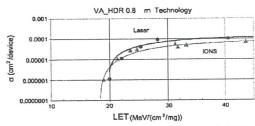

| -"LASER SYSTEM FOR SINGLE EVENT EFFECT TESTING AND RADIATION SENSITIVITY MAPPING OF INTEGRATED CIRCUITS",  M. Petasecca, B. Alpat, R. Battiston, M. Bizzarri, S. Blasko, M. T. Brunetti, D. Caraffini,  L. Di Masso, L. Farnesini, E. M. Fiori, M. Menichelli, A. Papi, V. Postolache, G. Scolieri, A. Secchi                                | 47       |

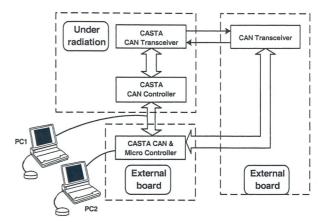

| -"CAN BUS PHYSICAL LAYER RADIATION TEST",<br>S. Chicca, F. Bigongiari, W. Errico, F. Bertuccelli , M. Lippi ,G. Manoni, M. Ceschia                                                                                                                                                                                                           | 50       |

| -"SINGLE EVENT EFFECTS IN SRAM-BASED FPGAS", M. Ceschia, M. Violante, M. Sonza Reorda, A. Paccagnella, P. Bernardi, M. Rebaudengo, D. Bortolato, M. Bellato, P. Zambolin                                                                                                                                                                     | 53       |

## SESSION III: RADIATION-HARD TECHNOLOGIES FOR ELECTRONICS IN HIGH ENERGY PHYSICS AND ASTROPHYSICS EXPERIMENTS

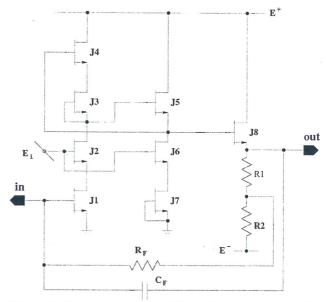

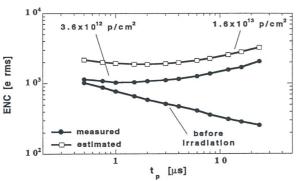

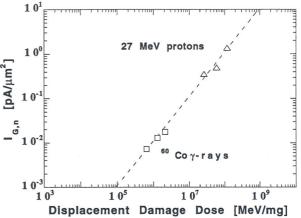

| -"BULK DAMAGE IN PROTON IRRADIATED JFET AND JFET-BASED CHARGE SENSITIVE AMPLIFIERS ON HIGH RESISTIVITY SILICON",                                                                                                                                                                |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| L. Ratti, GF. Dalla Betta, M. Manghisoni, V. Re, V. Speziali, G. Traversi, A. Candelori                                                                                                                                                                                         | 59 |

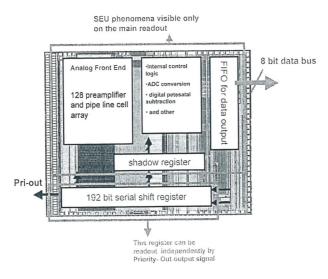

| -"SINGLE EVENT UPSET MEASUREMENTS ON THE SVX4 CHIP", N. Bacchetta, D. Pantano, Z. Wang                                                                                                                                                                                          | 63 |

| -"HEAVY ION IRRADIATION OF THE XAA1.2 ASIC CHIP FOR SPACE APPLICATIONS",<br>E. Del Monte, L. Pacciani, G. Porrovecchio, P. Soffitta, E. Costa, G. Di Persio, M. Feroci,<br>M. Mastropietro, E. Morelli, M. Rapisarda, A. Rubini, D. Bisello, A. Candelori, A. Kaminski, J. Wyss | 67 |

| -"RADIATION TESTING OF THE GLAST LAT TRACKER ASICS",<br>R. Rando, A. Bangert, D. Bisello, A. Candelori, P. Giubilato, M. Hirayama, R. Johnson,<br>H. FW. Sadrozinski, M. Sugizaki, J. Wyss, M. Ziegler                                                                          | 71 |

| -"RADIATION HARDNESS QUALIFICATION OF THE APV25 CHIP PRODUCTION FOR THE CMS EXPERIMENT", A. Candelori, R. Bainbridge, P. Barrillon, D. Bisello, M. J. French, G. Hall, A. Kaminski, V. Khomenkov, E. Noah, M. Raymond, L. Stefanutti, M. Tessaro                                | 75 |

| SESSION IV: FACILITIES FOR RADIATION TESTING OF DETECTORS AND ELECTRONIC DEVICES                                                                                                                                                                                                |    |

| -"Facilities for radiation hardness qualifications at ENEA-Casaccia",<br>S. Baccaro, A. Cecilia                                                                                                                                                                                 | 81 |

| -"The electron accelerator of the ISOF-CNR Institute and its use for industrial applications and applied research", <i>P. Fuochi, U. Corda, M. Lavalle</i>                                                                                                                      | 85 |

| -"THE PADOVA LABORATORY FOR INTERDISCIPLINARY APPLICATION OF NEUTRONS", G. Viesti, M. Cinausero, M. Lunardon, G. Nebbia, S. Pesente                                                                                                                                             | 88 |

| -"THE SIRAD IRRADIATION FACILITY FOR BULK DAMAGE AND SINGLE EVENT EFFECT STUDIES", A. Candelori, D. Bisello, P. Giubilato, A. Kaminski, D. Pantano, R. Rando, M. Tessaro, J. Wyss                                                                                               | 91 |

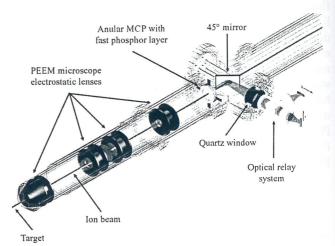

| -"THE ION ELECTRON EMISSION MICROSCOPE FOR SINGLE EVENT EFFECT STUDIES AT SIRAD",<br>D. Bisello, P. Giubilato, M. Nigro, R. Rando, J. Wyss, A. Candelori                                                                                                                        | 96 |

## SESSION I RADIATION HARDENING OF SILICON DETECTORS

## Status of the development of ultra radiation-hard semiconductor detectors for very high luminosity colliders

M. Bruzzi on behalf of the RD50 Collaboration

INFN Sezione di Firenze and Dipartimento di Energetica, Università di Firenze, Via S. Marta 3, Firenze, I-50139, Italy

#### I. INTRODUCTION

The luminosity upgrade to 10<sup>35</sup> cm<sup>-2</sup>×s<sup>-1</sup>, recently discussed to extend the High Energy Physics research at the Large Hadron Collider (LHC) [1], will require the development of ultra radiation hard semiconductor detectors, able to withstand fast hadron fluences up to 10<sup>16</sup> cm<sup>-2</sup>. The CERN RD50 Collaboration [2], "Development of Radiation Hard Semiconductor Devices for Very High Luminosity Colliders", started in 2002 with the aim to develop a new reliable detector technology available for the LHC upgrade or a future high luminosity hadron collider. Two main research lines have been identified: 1) Material Engineering, with the aim to produce the most intrinsically radiation hard semiconductor material in terms of degradation of the electrical properties after irradiation; 2) Device Engineering, to identify the best geometry (size and position) of the segmented electrodes in order to optimize the radiation resistance of the detector. The activity and the most recent advances of each research line are presented and discussed in this paper.

#### II. MATERIAL ENGINEERING

This research line is divided into three projects: Defect/Material Characterization (DMC), Defect Engineering (DE) and development of New Materials (NM). The DMC project relies on the detailed study of the microscopic aspects of radiation damage in the semiconductor bulk. Defect Engineering is focussed on the beneficial effect on radiation hardness due to the deliberate addition of selected impurities in the material. The NM project aim is to investigate novel radiation hard semiconductor materials. In this section a review on the most important advances of these projects is presented.

#### II.A. Defect/Material Characterization

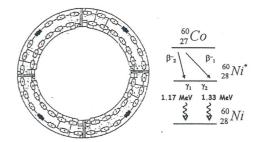

Particles impinging on the semiconductor bulk produce a cascade of primary defects (vacancies (V) and interstitials (I)). They migrate in the lattice and interact with each other or with the existing impurities, creating stable localized defect complexes (point defects) or extended damaged regions (clusters). The ratio of the clusters over point defects depends on the particle type and energy: only point defects are generated by  $^{60}\text{Co}\,\gamma$ -ray irradiation; both types of defects are created with hadron irradiation; while clusters are dominating the microscopic disorder after fast neutron irradiation [3]. Electrically active defects are responsible of the change in the main macroscopic properties of the particle

detectors: the effective doping concentration of the space charge region (Neff), the full depletion voltage (Vdep), the reverse current at full depletion (Ileak) and the charge collection efficiency (CCE). Thus, a first fundamental step for the definition of the optimal radiation hardening procedure is represented by the exhaustive identification of native and radiation-induced defects, and of their influence on the carrier transport properties in the device. The main tools available for studying defects are Deep Level Transient Spectroscopy (DLTS), Thermally Stimulated Current (TSC) and Photo Induced Transient Spectroscopy (PITS). These techniques are used to determine the activation energy and capture cross sections of the electrically active levels in the forbidden gap and to evaluate the concentration of the related defects in the semiconductor bulk. For the trap identification, the results are compared with the defect signature from a database of parameters of earlier identified defects.

Native or process-induced defects are quite important, as they can directly influence the  $N_{\text{eff}}$  value before irradiation: particularly, this is the case of thermal donors (TD) in Czochralski (Cz) silicon (Si). The RD50 Collaboration investigated in detail the thermal processes to enhance and/or to suppress TD generation, in view to control the  $N_{\text{eff}}$  of Cz Si-based diodes before irradiation. A donor killing process can be applied in order to partially deactivate the thermal donors in standard Cz Si and ensure a sufficiently high resistivity material.

Recently, important advancements in understanding the radiation damage in the case of point defects have been performed within the RD50 Collaboration. Point defects are of crucial importance for the radiation hardness of silicon after irradiation with <sup>60</sup>Co γ-rays. Three levels have been correlated with the changes of  $N_{\text{eff}},\,V_{\text{dep}}$  and  $I_{\text{leak}}$ : two midgap acceptor levels (I and  $\Gamma$  ) and a bistable donor (BD). I and  $\Gamma$  are generated in higher concentrations in standard Float Zone (FZ) silicon than in oxygen enriched Si, while the BD is mainly found in oxygen enriched and epitaxial silicon [4],[5]. The  $\Gamma$ defect, an acceptor level at E<sub>v</sub>+0.68 eV, is characterized by linear dose dependence, and it can explain about 10% of the damage. The I defect, of amphoteric nature, having both an acceptor state at Ec-0.54 eV and a donor state at E<sub>v</sub>+0.23 eV, has a quadratic dose dependence and it is proven to be the main cause for the space charge sign inversion in standard FZ diodes. The I defect accounts for more than 85% of the damage caused by γ-ray irradiation.

#### II.B. Defect Engineering of Silicon

Since 1995 the RD48 CERN Collaboration [6] has adopted the strategy to add selected impurities in the

silicon bulk in order to beneficially influence the microscopic damage induced by radiation. The key idea in the RD48 proposal was in particular to investigate the influence of oxygen on the silicon radiation hardness. The concentration of interstitial oxygen in Si ([Oi]) is strongly dependent on the growth technique. In high purity Float Zone silicon [O<sub>i</sub>]~10<sup>15</sup> cm<sup>-3</sup>, while in Czochralski silicon [O<sub>i</sub>] can reach values as high as 10<sup>18</sup> cm<sup>-3</sup>. The first attempt in the High Energy Physics Community to enrich silicon wafers with oxygen for radiation hardening purposes was made in 1992 at the Brookhaven National Laboratory [7]. As at that time Czochralski silicon was not available with the high resistivity required for a proper application in tracking detectors, an opportune technique was developed to produce Diffusion Oxygenated Float Zone (DOFZ) silicon. By this method silicon was doped with oxygen by high temperature (1200°C) oxidation during 20 to 220 hours, to obtain the Oi concentration of the order of  $2 \times 10^{17} \text{ cm}^{-3}$ .

High resistivity Cz Si suitable for detector applications became recently available after proper developments in the crystal growth techniques (see e.g. [8]). Two different Cz materials are under investigation in the framework of the RD50 Collaboration: Magnetic Czochralski (MCz) from Okmetic Ltd (Finland) and standard Cz (SCz) material from Sumitomo-Sitix (Japan). The first material has a resistivity of  $\approx 900~\Omega \times cm$  and an oxygen concentration of  $3.5 \times 10^{17}~cm^{-3}$ ; the second material has a resistivity of  $\approx 1200~\Omega \times cm$  and an oxygen concentration of  $8 \times 10^{17}~cm^{-3}$ .

A different approach for increasing the radiation tolerance of silicon detectors is the use of thin epitaxial silicon layers. Single crystal epitaxial layers of different resistivity and thickness can be grown on different substrates (Cz, FZ). Low resistivity (50  $\Omega \times \text{cm}$ ) 50  $\mu \text{m}$  thick epitaxial layers were grown by ITME (Poland) on low resistivity (0.015  $\Omega \times \text{cm}$ ) Cz substrates [9].

#### II.C. New Materials

SiC and GaN, which have physical properties in between those of Si and diamond, can be attractive materials for particle detection. Due to the low leakage current, almost insensitive to radiation, ( $\approx 10^{-10} \text{A/cm}^2$ ), they are potentially radiation-hard.

Preliminary results with α-particles from a  $^{241}$ Am source evidence a 60% CCE for semi-insulating SiC, which is reduced to  $\approx 50\%$  after irradiation by 300 MeV pions up to  $10^{13}$  cm<sup>-2</sup> [10]. A 100% CCE was measured with β-particles from a  $^{90}$ Sr source on 4H-SiC Schottky diodes manufactured with n-type epitaxial wafers (IKZ, Berlin): the measured signal, stable and reproducible, is  $\approx 2200$  electrons in the thickest epitaxial layer ( $\approx 40 \mu m$ ) [11].

In preliminary tests with  $\alpha$ -particles from a <sup>241</sup>Am source on semi-insulating GaN Schottky detectors the CCE reduced from 92% to 77% after irradiation by nuclear reactor neutrons up to  $5\times10^{14}$  cm<sup>-2</sup> [12]. More studies are still necessary to definitely assess the radiation hardness of these materials as compared to Si.

#### III. DEVICE ENGINEERING

This research line is divided into three projects: Pad Detector Characterization (PDC), New Structures (NS) and Full Detector Systems (FDS). The PDC project deals with radiation damage studies performed with the simplified geometry of a single pad detector (SPD), i.e. a single-pad p<sup>+</sup>-n-n<sup>+</sup> structure surrounded by a set of guardrings. The FDS project is focused on radiation damage studies on prototype microstrip and pixel detector modules with LHC-like read-out electronics, while the NS main research activity is to develop novel detector geometries to increase the device radiation hardness. In this section a review on the most important recent results of these three projects is presented.

#### III.A. Pad Detector Characterization

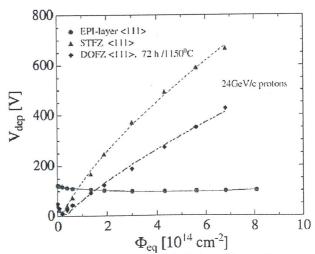

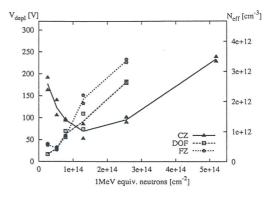

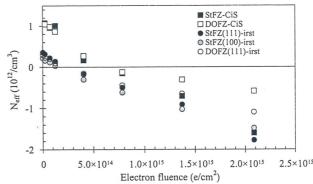

The use of SPD provides the cost-effective development of radiation tests mainly concentrated on the study of parameters (Neff, Vdep, Ileak, CCE) as a function of the particle fluence. The radiation hardness of SPD made with defect engineered Si (DOFZ, Cz, MCz, and epitaxial) has been investigated by several irradiation campaigns at different facilities, with different particles and energies. These devices exhibit interesting radiation hardness properties [9],[13],[14]. In particular, for Cz Si there is no type inversion after irradiation with 190 MeV pions (PSI) or 24 GeV/c protons (CERN) up to 1015 particles/cm<sup>2</sup>. The change of V<sub>dep</sub> as function of fluence is considerably smaller than that of standard FZ or DOFZ silicon devices. The epitaxial diodes show superior radiation tolerance compared to those fabricated with all the other silicon materials. Fig.1 shows a comparison between epitaxial diodes and diodes fabricated with standard FZ (STFZ) and DOFZ materials. In the full range of the measured fluences rescaled to 1 MeV equivalent neutrons up to  $8\times10^{14}$  cm<sup>-2</sup>, the epitaxial diodes do not exhibit the space charge sign inversion and show a reduced variation of the full depletion voltage [9].

Figure 1. Comparison of the depletion voltage  $(V_{dep})$  as a function of the 24 GeV/c proton fluence rescaled to 1 MeV equivalent neutrons  $(\Phi_{eq})$  for diodes manufactured on different silicon substrates [9].

#### III.B. New Structures

In standard detector geometry, electrodes are placed on opposite sides of the semiconductor, as in parallel plate capacitor geometry. The charge generated by ionizing radiation drifts in the direction perpendicular to the plane of the semiconductor wafer to the oppositely biased electrodes. The charge generated by the impinging radiation is proportional to the sensitive thickness of the detector, therefore to the detector thickness when the device is fully depleted. When the detector suffers high radiation damage, the full depletion cannot be achieved anymore and the charge trapping further reduces the amount of the collected charge drifting for longer distances.

A novel type of device, called 3D detector, was introduced [15] to reduce the electrode distance, therefore increasing the amount of charge collected after heavy irradiation, while keeping the same detector thickness. In 3D devices, the generated charge drifts in the plane of the wafer and the electrode separation is independent of the material thickness. Thus, the 3D geometry may be designed to both maximize signal response to incident radiation and minimize sensitivity to defects arising from radiation damage.

Three different routes to fabricate the 3D geometries have been developed. Depending on particular material system and requirements, one or other of these methods is to be preferred. The electrodes may be produced using plasma etching (micro-machining), femtosecond laser drilling technique, or photo-electrochemical (PEC) etching.

The plasma etching technique is the most compatible with micro-fabrication processes. However, for 3D detector manufacture it is suitable only for silicon and is currently limited to an aspect (depth-to-width) ratio for the holes of about 20:1. PEC will in principle produce holes of arbitrary aspect ratio, but the geometries usable are more limited due to the nature of the process. The laser drilling technique is the most cumbersome, as each electrode is made in sequence. In silicon, plasma etching and PEC produce electrodes in parallel, so both those methods are best suited for volume production of 3D detectors. Plasma etching and laser machining are independent of crystal orientation. PEC is suitable only for specific crystal orientations, which are easily commercially available. The electrodes are then formed in these vias and connected to the read out electronics with deposited metal lines and contacts. Besides the 3D detectors, now developed within RD50 by ITC-irst (Trento), CNM (Barcelona) and Glasgow University, other new geometries are under investigation, namely thin detectors [16] and semi-3D devices [17]. The status of these activities can be found in [18].

#### III.C. Full Detector Systems

The FDS research line of RD50 aims to test the properties of segmented detectors after heavy irradiation in order to allow the choice of the optimal geometry (diode structure, detector thickness, cell size, and so on) for the targeted radiation fluence and to validate the use of non-standard silicon substrates for the production of

large area segmented devices. The crucial parameter which defines the ability of the detector to provide the tracking information is the signal to noise ratio. The noise is dependent on the particular setup used to readout the detectors, thus it is important that the detector charge collection efficiency as a function of the reverse bias voltage (i.e., CCE(V)) is evaluated with a LHC-like read-out electronics at the speed of 40 MHz.

CCE(V) of irradiated silicon detectors depends on trap density and on collection time  $(t_c)$ , therefore on the drift velocity of the charge carriers. The amount of the trapped charge is inversely proportional to  $t_c$ . The charge carrier velocity  $\nu$  depends on the local electric field E(x), i.e.  $v=\mu_{e,h}\times E(x)$  where  $\mu$  is the mobility for electrons (e) and holes (h), until the saturation velocity is achieved. As a consequence, a lower trapping is expected for carriers moving in high electric field (smaller  $t_c$ ).

Silicon detectors are usually manufactured by implanting high doped p-type strips on high resistivity n-type substrates. An ohmic contact (high doped n-type) is implanted on the backplane (p-in-n diode). After space charge sign inversion the junction and consequently the high electric field migrate on the backplane contact and a better charge collection is obtained by segmenting the n-type implant (n-in-n detectors) [19],[20]. The n-side read out can be implemented on n-type or p-type substrates. The use of p-type substrates has the advantages of avoiding substrate type inversion and providing the cheapest processing cost, due to the possibility of one side processing, compared to the double side processing required by n-type silicon substrates.

In a previous study [21], a substantial improvement of the charge collection after irradiation at low bias voltages was observed for standard p-type substrates read-out at the n-side (n-in-p detectors) when compared to p-type substrates read-out at the p-side (p-in-n detectors) [21].

A possible further improvement of the radiation hardness could be obtained with oxygen enriched p-type substrates. The Liverpool University and CNM (Barcelona, Spain) investigated in the framework of the RD50 Collaboration, the charge collection properties of n-in-p microstrip detectors manufacture on oxygenated substrates, comparing their performances with devices produced on p-in-n standard and oxygenated silicon [22]. Standard (oxygenated) detectors were irradiated with 24 GeV/c protons at CERN up to 3×1015 protons/cm2  $(7.5\times10^{15} \text{ protons/cm}^2)$ . The main result was that even after the highest irradiation fluence, the charge collection of the n-in-p detectors manufactured on oxygenated silicon is higher than 6500 electrons at the maximum applied bias (900 V) [22]. This corresponds to a signal to noise ratio of ≈7.5, which could still be sufficient for efficient tracking. Further studies are required to investigate whether the oxygenation of p-type substrates brings any advantage, but such detectors appear to be suitable for being used as particle detectors also after experiencing extremely high level of fast hadron fluences.

<sup>&</sup>quot;Physics potential and experimental challenges of the LHC luminosity upgrade", CERN-TH/2002-078.

- [2] "Development of radiation hard semiconductor devices for very high luminosity colliders", LHCC 2002-003, 15 February 2002, CERN, Geneve.

- [3] M. Huhtinen, Nucl. Instr. Meth., A491 (2002) 194.

- [4] I. Pintilie et al., Appl. Phys. Lett., 82 (2003) 2169.

- [5] I. Pintilie et al., Nucl. Instr. Meth., A514 (2003) 18.

- [6] RD48. On line available: http://rd48.web.cern.ch/rd48/.

- [7] Z. Li et al., IEEE Trans. Nucl. Sci., 42 (1995) 219.

- [8] V. Savolainen et al., J. Crystal. Growth, 2 (2002) 243.

- [9] G. Kramberger et al., Nucl. Instr. Meth., A515 (2003) 665.

- [10] W. Cunningham et al., Nucl. Instr. Meth., A509 (2003) 127.

- [11] F. Nava et al., IEEE Trans. Nucl. Sci., 51 (2004) 238.

- [12] J. Vaitkus et al., Nucl. Instr. Meth., A514 (2003) 141.

- [13] J. Härkönen et al., Nucl. Instr. Meth., A518 (2004) 346.

- [14] G. Lindström et al., "Recent damage results from the HH-CiS collaboration", 1st RD50 Workshop on Radiation Hard Semiconductor Devices for Very High Luminosity Colliders, CERN, 2-4 October 2002. On line available: http://www.cern.ch/rd50.

- [15] S. I. Parker et al., Nucl. Instr. Meth., A395 (1997) 328.

- [16]Z. Li, "Activities of the US chapter of CERN RD50 on the development of semi-3D Si detectors", 2<sup>nd</sup> RD50 Workshop on Radiation Hard Semiconductor Devices for Very High Luminosity Colliders, CERN, 18-20 May 2003. On line available: http://www.cern.ch/rd50.

- [17]S. Ronchin et al., "Fabrication of PIN diodes on thinned high resistivity silicon", 6<sup>th</sup> International Conference on Large Scale Applications and Radiation Hardness of Semiconductor Detectors, Firenze, Italy, 29 September-1 October 2003.

- [18] On line available: http://www.cern.ch/rd50/.

- [19] G. Casse et al., Nucl. Instr. Meth., A511 (2003) 112.

- [20] G. Casse et al., IEEE Trans. Nucl. Sci., 47 (2000) 527.

- [21] G. Casse, "First results with oxygenated n-in-p detectors after irradiation", 2<sup>nd</sup> RD50 Workshop on Radiation Hard Semiconductor Devices for Very High Luminosity Colliders, CERN, 18-20 May 2003. On line available: http://www.cern.ch/rd50.

- [22] G. Casse et al., "Performances of miniature microstrip detectors made on oxygen enriched p-type substrates after very high proton irradiation", presented at the 10<sup>th</sup> Vienna Conference on Instrumentations, Vienna, Austria, 16-21 Febrary 2004.

#### Radiation damage measurements for the ALICE pixel detectors

M. Cinausero<sup>1</sup>, E. Fioretto<sup>1</sup>, G. Prete<sup>1</sup>, L. Vannucci<sup>1</sup>, F. Antinori<sup>2</sup>, R. Dima<sup>2</sup>, D. Fabris<sup>2</sup>, M. Lunardon<sup>2</sup>, S. Martini<sup>2</sup>, S. Moretto<sup>2</sup>, A. Pepato<sup>2</sup>, F. Scarlassara<sup>2</sup>, G. Segato<sup>2</sup>, F. Soramel<sup>2</sup>, R. Turrisi<sup>2</sup>, G. Viesti<sup>2</sup>, A. Candelori<sup>2</sup>, D. Bisello<sup>2</sup>, A. Kaminski<sup>2</sup>, D. Pantano<sup>2</sup>, P. Riedler<sup>3</sup>, G. Stefanini<sup>3</sup>

<sup>1</sup>INFN Laboratori Nazionali di Legnaro, Viale dell'Università 2, Legnaro (Padova), I-35020, Italy

<sup>2</sup> INFN Sezione di Padova and Dipartimento di Fisica, Università di Padova, Via Marzolo 8, Padova, I-35131, Italy

<sup>3</sup>CERN, Geneva, Switzerland

#### I. INTRODUCTION

ALICE is an experiment presently under construction at the CERN Large Hadron Collider (LHC). It is primarily designed to investigate the behaviour of strongly interacting matter under the extreme conditions of heating and compression that will be reached in ultrarelativistic nucleus—nucleus collisions at the energy of the LHC. The ALICE experimental apparatus is described in [1].

The inner region, with a radius of about 0.45 m, will be instrumented with the Inner Tracking System (ITS) [2],[3] providing high precision, high granularity tracking close to the primary interaction vertex for the detection of weak decays of strange, charm and beauty particles. The ITS will allow full tracking in the pseudorapidity range  $|\eta|<1$  and a measurement of the charged multiplicity out to  $|\eta|<2$ . It will consist of six concentric layers of silicon detectors: two layers of Silicon Pixel Detectors (SPD), two layers of Silicon Drift Detectors (SDD) and two layers of Silicon Strip Detectors (SSD).

Physics performance constraints have determined the choice of carbon fibre for the support structure, aluminium-based technology for the flex circuitry and low thickness for the silicon sensors and integrated circuits. A description of the status of the ITS system is given in [4].

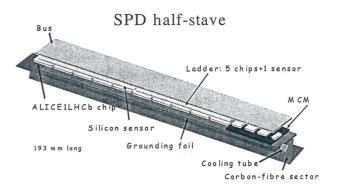

The SPD will consist of two barrel layers of silicon pixel detectors located at 39 mm and 76 mm from the beam line. The sensitive length along the beam direction will be 286 mm. Each detector module (ladder) consists of a silicon sensor having a sensitive area of 12.8 mm ( $r\phi$ ) × 69.6 mm (z). It includes 256 ( $r\phi$ ) × 160 (z) cells each measuring 50  $\mu$ m ( $r\phi$ ) × 425  $\mu$ m (z). Each cell is bump-bonded to a contact of the ALICE1LHCb read-out chip: five chips are used for each ladder. The target thickness for the sensor-chip assembly is 350  $\mu$ m. Two ladders are mounted along the beam direction to form a 143 mm long Half Stave (HS) [5], as shown in Fig.1.

An aluminium-polyamide multi-layer flex (the pixel bus) containing both data control bus and power lines is glued to the sensors and wire bonded to the read-out chips. A thin Al-kapton (25+50  $\mu \rm m$  thickness) grounding foil will also be glued to the chips. The assembled HS will be mounted on a Carbon Fibre Support Sector (CFSS) and cooling sector. Each CFSS holds four outer layer Staves and two inner layer Staves. Ten Sectors are mounted around the beam pipe to form the full barrel

which therefore consists of 60 Staves, 240 ladders, 1200 chips, and  $\approx 10^7$  pixel cells. The average material crossed by a particle hitting perpendicularly to the SPD will correspond to about 2% of a radiation length. The current status of the SPD project has been presented in [6].

Due to the close proximity of the SPD to the beam, radiation-induced effects cannot be neglected. All readout and control chips have been designed employing radiation-tolerant design techniques, and the behaviour of the SPD sensors under irradiation has been studied using X-rays and proton beams. The purpose of the present paper is the study of the proton irradiation effects on the ALICE SPD sensor performed at the SIRAD irradiation facility of the INFN National Laboratory of Legnaro (Padova, Italy).

Figure 1. The ALICE SPD Half Stave.

#### II. EXPECTED RADIATION LEVELS

The expected values of the dose and the equivalent fluence referred to 1 MeV neutrons accumulated at the SPD layers in 10 years of operation are reported in Table I. These values were calculated by means of a FLUKA simulation [7] assuming the standard running scenario of ALICE, with 10<sup>8</sup> proton-proton interactions/s, 5×10<sup>6</sup> Pb-Pb interactions/s and 10<sup>6</sup> Ar-Ar interactions/s, each at the expected nominal value of the luminosity. The estimated uncertainty on the results is about 30%.

Given the uncertainty of these estimates and possible changes in the planning of the ALICE activity, for the present study we took the precaution of doubling the value of the estimated maximum fluence to  $\approx 6 \times 10^{12}$   $n_{eq}/cm^2$ , where  $n_{eq}$  refers to 1 MeV equivalent neutrons.

TABLE I. IRRADIATION LEVEL OF THE SPD DETECTORS IN 10 YEARS OF ALICE ACTIVITY.

|             | Dose<br>(Gy(Si))    | Dose (krad(Si)) | Fluence (1 MeV equivalent n/cm²) |

|-------------|---------------------|-----------------|----------------------------------|

| SPD layer 1 | $2.5 \times 10^{3}$ | 250             | $2.95 \times 10^{12}$            |

| SPD layer 2 | 5.2×10 <sup>2</sup> | 52              | 1.30×10 <sup>12</sup>            |

#### III. SPD SENSOR IRRADIATION

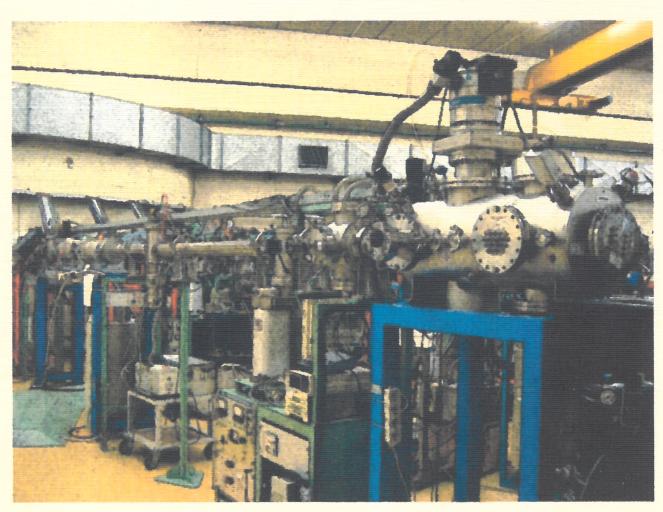

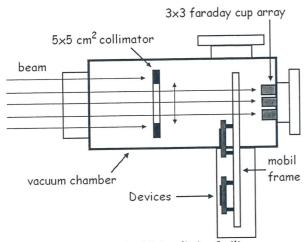

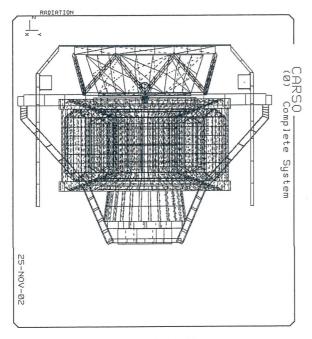

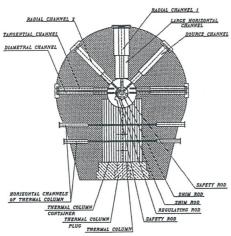

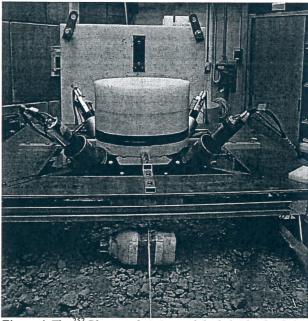

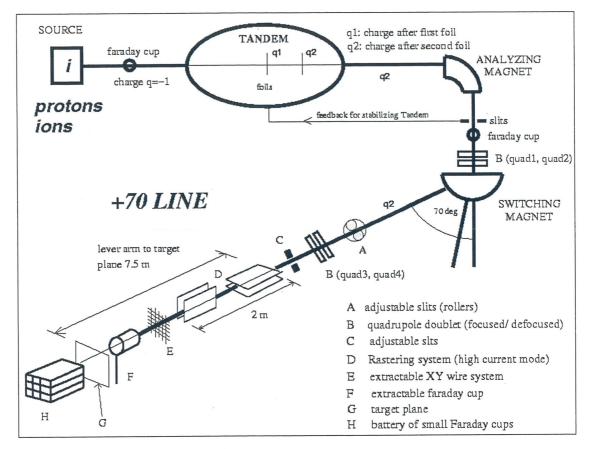

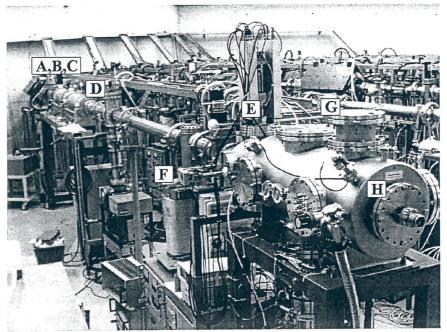

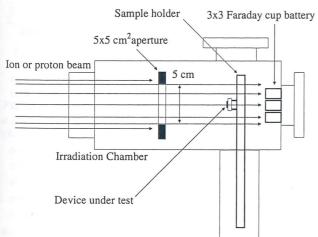

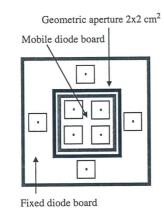

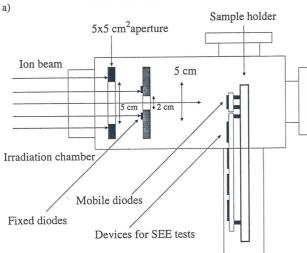

The SPD were irradiated at the SIRAD irradiation facility by a 27-MeV proton beam delivered from the Tandem-XTU accelerator of the INFN National Laboratory of Legnaro. The sensors were mounted on a mobile frame inside the vacuum chamber (see Fig.2) in order to easily change the devices exposed to the beam. The proton beam was rastered with uniformity of 7% on a  $5\times5$  cm<sup>2</sup> area. The flux during irradiation was set to  $\approx10^8$ - $10^9$  protons/(cm<sup>2</sup>×s).

The displacement damage is observed when atoms of the lattice structure are displaced from their original position by impinging particles on the silicon crystal. The sensor radiation damage was referred to the displacement damage induced by 1 MeV neutrons rescaling the fluences for 27 MeV protons to 1 MeV neutrons by the 27 MeV proton hardness factor K(p) calculated as follows:

$$K(p) = \frac{1}{D(n)} \frac{\int D(p, E) \cdot S(p, E) dE}{\int S(p, E) dE}$$

(1)

where n and p indicate 1 MeV neutrons and 27 MeV protons, respectively, E is the energy, S is the energy spectrum, D is the displacement damage cross section, and D(n)=95 MeV×mb. The obtained value for the hardness factor of 27 MeV protons was  $K(p)\approx 2$ .

Figure 2. Scheme of the SIRAD irradiation facility.

#### IV. SPD DIODE CHARACTERIZATION

The radiation damage induces microscopic defects in the detector substrate, which cause variations of the sensor characteristics at macroscopic level. In particular, radiation-induced defects at midgap of the Si valence and conduction bands cause an increase of the leakage current; donor compensation and deep acceptor generation by radiation produce variations of the depletion voltage; the electron-hole pair recombination and the trapping of charge carriers reduce the charge collection efficiency. For this reason the level of the radiation damage can be evaluated by the comparison of the leakage current and of the depletion voltage before and after irradiation.

Figure 3. Diode characterization at CERN.

TABLE II. DIODE CHARACTERIZATION IN PADOVA.

|           | I <sub>diode</sub> at I <sub>diode</sub> at Temperature |                          | $V_{dep}$ |     |

|-----------|---------------------------------------------------------|--------------------------|-----------|-----|

|           | V <sub>bias</sub> =50 V                                 | V <sub>bias</sub> =100 V | (°C)      | (V) |

|           | (nA)                                                    | (nA)                     |           |     |

| 1#1-63-p  | 100                                                     | 2000                     | 23.9      | ≈29 |

| 1#2-68    | 5.5                                                     | 401                      | 24.2      | ≈17 |

| 1#263p    | 6                                                       | 6.9                      | 24.1      | ≈18 |

| 1#2-68#2  | 13.5                                                    | 35.7                     | 24.0      | ≈17 |

| 1#2-63r   | 4.1                                                     | 6.2                      | 24.1      | ≈18 |

| 1#2-63r#2 | 6.5                                                     | 90.9                     | 24.0      | ≈18 |

| 1#2-63p#2 | 5.7                                                     | 8.3                      | 24.1      | ≈20 |

All the sensors where electrically characterized before irradiation. A first set of 7 diodes, with thickness of 300  $\mu$ m, was wire-bonded in order to bias the devices during irradiation. For this reason the electrical characterization was performed at CERN before shipping (Fig.6), after wire-bonding in Padova (Table II), and finally also at the INFN National Laboratory of Legnaro by using a  $^{241}$ Am  $\alpha$  source.

The results of the electrical characterizations before irradiation are mutually in agreement, showing low leakage currents (some nA) and depletion voltage  $V_{\text{dep}} \approx 20 \text{ V}$ .

A second set of diodes, with thickness of 200  $\mu$ m, was exposed unbiased to the proton beam, i.e. without wire-bonding. In this case the electrical characterization was performed by contacting the diodes with needles of a probing setup. The leakage current and the full depletion voltage of the 200  $\mu$ m thick sensors, when rescaled for the different thickness, are similar to the values measured for the 300  $\mu$ m thick devices.

## V. IRRADIATION EFFECTS ON THE ALICE SILICON PIXEL DETECTORS

The effective substrate doping concentration ( $N_{\text{eff}}$ ) depends on the detector depletion voltage ( $V_{\text{dep}}$ ) as

$$\left| N_{\text{eff}} \right| = \frac{2\varepsilon}{qW^2} \left( V_{\text{dep}} - V_{\text{bi}} \right) \tag{2}$$

where q is the electron charge, W is the detector thickness,  $\varepsilon$  is the absolute silicon dielectric constant, and  $V_{bi}$  is the silicon built-in potential.

At the beginning of irradiation,  $N_{eff}>0$  starts to decrease up to reach the Space Charge Sign Inversion (SCSI), i.e. when the substrate type inversion from "n-type" to "p-type" takes place and  $N_{eff}$  becomes negative. For fluence values beyond SCSI,  $|N_{eff}|$  and consequently  $V_{dep}$  increase monotonically.

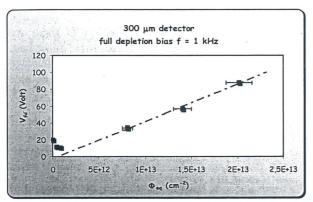

Figure 4. Depletion voltage for the 300  $\mu$ m thick detectors as a function of the 1 MeV equivalent neutron fluence.

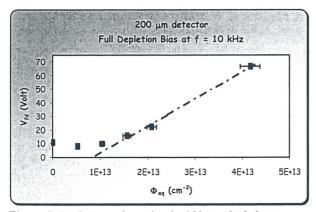

Figure 5. Depletion voltage for the 200 µm thick detectors as a function of the 1 MeV equivalent neutron fluence.

This trend characterizes also the ALICE SPD sensors. The two sets of diodes, with 200  $\mu m$  and 300  $\mu m$  thickness, have the SCSI point (see Fig.4 and Fig.5) at an equivalent fluence  $\Phi_{eq} \approx 3\text{-}4\times 10^{12}~n_{eq}/\text{cm}^2$ . This value roughly corresponds to the maximum fluence expected for the SPD in the 10 years of ALICE activity. We remark that even at the precautionary irradiation level for the ALICE SPD, i.e.  $\approx 6\times 10^{12}~n_{eq}/\text{cm}^2$ , the depletion voltage remains similar to the value before irradiation.

The second parameter considered to evaluate the radiation damage is the leakage current increase, which depends on the detector active volume and temperature. A more convenient parameter is consequently the

leakage current density J(T), i.e. the ratio between the leakage current at  $V_{\text{dep}}$  and the detector volume, which can be rescaled with temperature by

$$J(T_R) = J(T) \left(\frac{T_R}{T}\right)^2 exp\left(-\frac{E}{2k_B} \left\lceil \frac{1}{T_R} - \frac{1}{T} \right\rceil\right)$$

(3)

where T is the absolute temperature during the leakage current measurement,  $T_R$  is the reference temperature (usually 293.16 K), E is equal to 1.24 eV and  $k_B$  is Boltzmann's constant.

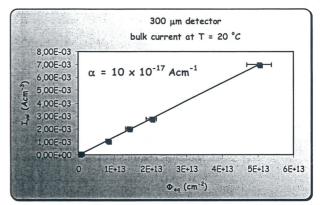

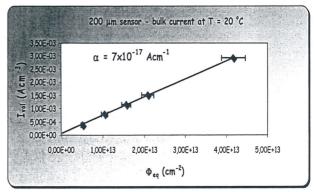

Figure 6. Leakage current density for the 300 µm thick detectors as a function of the 1 MeV equivalent neutron fluence.

Figure 7. Leakage current density for the 200 µm thick detectors as a function of the 1 MeV equivalent neutron fluence.

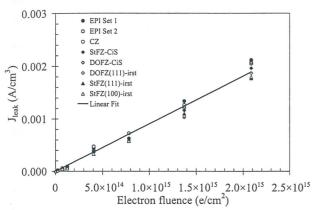

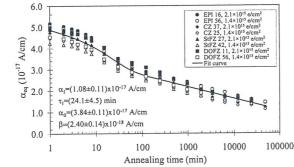

The leakage current density linearly increases as a function of the irradiation fluence

$$J_{IR} = J_0 + \alpha \times \Phi_{eq} \tag{4}$$

where  $J_0\left(J_{IR}\right)$  is the leakage current density before (after) irradiation and  $\alpha$  is leakage current density increase rate. The constant  $\alpha$  is also called damage parameter because, due to the Non-Ionizing Energy Loss scaling, it scales with the hardness factor K

$$\frac{\alpha(p)}{\alpha(n)} = \frac{K(p)}{K(n)}$$

(5)

and it directly correlates the radiation damage due to 27 MeV protons (p) to the one expected for 1 MeV neutrons (n).

The leakage current density as a function of the 1 MeV equivalent neutron fluence is reported in Fig.6 and in Fig.7 for the 300  $\mu$ m and 200  $\mu$ m thick detectors, respectively. The  $J_{IR}$  dependence as a function of  $\Phi_{eq}$  is linear, as expected. The  $\alpha$  value, i.e. the slope of the

linear fits in Fig.6 and in Fig.7, is about a factor two higher than the expected value of  $4\times10^{-17}$  A/cm after 30 days at room temperature because the leakage current measurements were performed just after irradiation and the detectors did not benefit for any annealing.

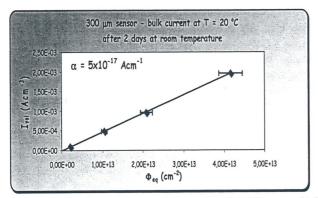

Figure 8. Leakage current density for the 300  $\mu$ m thick detectors as a function of the 1 MeV equivalent neutron fluence after 2 days at room temperature since the end of irradiation.

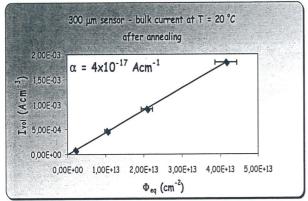

Figure 9. Leakage current density for the 300  $\mu$ m thick detectors as a function of the 1 MeV equivalent neutron fluence after 2 days at room temperature and 4 minutes of annealing at 80 °C.

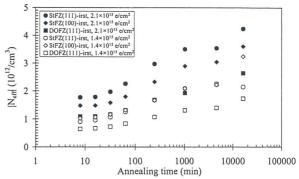

The annealing is a complex time-dependent process characterized both by positive and negative effects. The first class decreases the degradation induced in the detector by radiation, on the contrary the latter increases it. After irradiation the defects generated in the silicon lattice are not stable: vacancies are mobile and their mobility depends on temperature. So, the positive aspect is that, in principle, they can be removed. On the other, hand mobile defects can combine with impurities and other defects and generate new stable defects, which increase the degradation. The dynamics of the annealing is temperature dependent, therefore heating the detector can accelerate the annealing process and its evolution can be observed in a short time scale. In particular the effects produced heating the detector for 4 minutes at 80 °C roughly corresponds to the effects observed in 30 days at room temperature.

We studied the effect of the annealing on four ALICE SPD with thickness of 300  $\mu$ m, which were irradiated by 27 MeV protons at four different fluences: 1, 5, 10,  $20\times10^{12}$  protons/cm<sup>2</sup>. Fig.8 shows the leakage current density after 2 days of annealing at room temperature ( $\approx21^{\circ}$ C). The  $\alpha$  parameter is not as high as observed

immediately after irradiation (Fig.6), but still exceeds the expected value after 30 days at room temperature (4×10 $^{17}$  A/cm). After the heating treatment at 80 °C for 4 minutes corresponding to 30 days at room temperature (see Fig.12):  $\alpha$  nicely matches the expected 4×10 $^{-17}$  A/cm value.

This behaviour shows that most of the effect of the annealing takes places in the first hours after irradiation. Consequently the periodic sporadic irradiation of sensors at low fluence, as it happens in a real experiment, is expected to better preserve the detector functionality.

#### VI. CONCLUSIONS

The ALICE Silicon Pixel Detector needs to withstand an equivalent fluence up to  $6\times10^{12}\,\mathrm{n_{eq}/cm^2}$ . We have tested the effects of radiation on 200  $\mu\mathrm{m}$  and

We have tested the effects of radiation on 200  $\mu m$  and 300  $\mu m$  thick sensors by irradiating them at several fluences up to  $\Phi_{eq} = 6 \times 10^{12}~n_{eq}/cm^2$ , and in different conditions (biased and unbiased). For all of them we observed a trend of the radiation damage in agreement with what is expected from literature. Both the leakage current and the full depletion voltage remain acceptable at the maximum fluence value expected in the ALICE experiment.

<sup>[1]</sup> ALICE Collaboration, "Technical proposal", CERN/LHCC 95-71.

<sup>[2]</sup> ALICE Collaboration, "Inner tracking system technical design report", CERN/LHCC 99-12.

<sup>[3]</sup> ALICE Collaboration, "Physic performance report", CERN/LHCC 2003-049.

<sup>[4]</sup> F. Antinori, Nucl. Instr. Meth., A511 (2003) 215.

<sup>[5]</sup> M. Caselle et al., Nucl. Instr. Meth., A518 (2004) 297.

<sup>[6]</sup> G. Stefanini, Nucl. Instr. Meth., A530 (2004) 77.

<sup>[7]</sup> A. Morsch et al., "Radiation in ALICE detectors and electronic racks", ALICE-INT-2004-17 ver.1.

#### Development of Czochralski silicon particle detectors

J. Härkönen, P. Luukka, E. Tuovinen, E. Tuominen

Helsinki Institute of Physics, CERN Office, CERN/EP, CH-1211, Geneve 23, Switzerland

#### I. INTRODUCTION

Silicon detectors are widely used in High Energy Physics experiments because of their mature fabrication technology and favourable electrical properties. At the CERN Large Hadron Collider (LHC) experiments, detectors will be subjected to very hostile radiation environment. Unfortunately, this particle radiation causes irreversible crystallographic defects in silicon material thus inducing generation-recombination centres, which in turn result to an increase of the detector leakage current.

Additionally, crystallographic defects compensate the initial space charge of the silicon substrate [1], finally changing the conductivity from n- to p-type. Furthermore, silicon detectors are p-i-n diode structures designed to operate at full depletion with moderate reverse bias voltages (≈100-200 V). However, radiation induced defects lead to increase the depletion voltage. Thus, after high particle irradiation fluences, the breakdown voltage of the p-i-n structure may be reached before the full depletion.

High oxygen concentration demonstrably improves the radiation hardness of silicon detectors [2]. Particle detectors are traditionally processed on high resistivity Float Zone silicon (FZ-Si) that is fully depleted at reasonably low operating voltages but, on the other hand, has low oxygen concentration. FZ-Si can be oxygenated ([O]~10<sup>17</sup> cm<sup>-3</sup>) by long-term diffusion at high temperature. However, because of the contamination risk present in high temperature processes, the oxygenation is difficult to be implemented in large-scale production.

Recent developments in the crystal growth technology of Czochralski silicon (Cz-Si) have enabled the production of Cz-Si wafers with sufficiently high resistivity and with well-controlled high concentration of oxygen ([O]≈10<sup>18</sup> cm<sup>-3</sup>). In addition, using Cz-Si as detector material may offer economical benefits. Since Cz-Si wafers are available up to the diameter of 300 mm, very large area detectors could be manufactured. This could bring significant savings in the costs related to detector front-end electronics and module assembly.

We have processed detectors on silicon wafers grown by Magnetic Czochralski (MCz) method. The MCz method has several advantages. It extends the controllable range of oxygen dissolving from the silica crucible during the crystal growth. A magnetic field can be applied in the crystal growth system in order to damp the oscillations in the melt. The applied field creates an electric current distribution and an induced magnetic field in the electrically conducting melt. This produces a Lorentz force that influences the flow and reduces the amplitude of the melt fluctuations [3]. The n- and p-type Cz-Si wafers manufactured by Okmetic Ltd (Finland) have a nominal resistivity of ≈900 Ω×cm and ≈2000

$\Omega \times cm$  for n- and p-type silicon, respectively. The oxygen concentration is less than 10 atomic part per million (ppma).

#### II. DETECTOR PROCESSING

The high resistivity Cz-Si detectors can basically be processed into segmented or pad detectors in the same way as in the case of the traditionally used Fz-Si substrates. The process sequence is described in detail in [4]. The essential difference between Cz-Si and Fz-Si materials is, however, the oxygen concentration. It is well know that the aggregation of oxygen atoms will lead to the formation of electrically active defects, commonly named Thermal Donors (TD) [5-7]. The TDs are shallow donor levels within the energy range of 0.01-0.2 eV below the conduction band [8]. The formation of thermal donors is strongly dependent on the temperature and on the oxygen concentration in the silicon material. Heat treatment between 400-600 °C can yield to a TD concentration comparable to that of the background doping of high resistivity magnetic Cz-Si and thus to significant deviation in the full depletion voltages of the detectors. It has also been found that the presence of hydrogen in the detector fabrication process can enhance the generation of TDs [9].

The TD generation can be formulated by the

empirical equation [10]

$$N_{TD} = \left(\frac{a}{b}\right) C_{io}^{\chi} \frac{1}{\left|N_{d} - N_{A}\right|^{2}} \left\{1 - e^{-b \cdot D_{i} \cdot C_{io} \cdot t}\right\}$$

(1)

where a and b are experimental fitting parameters, Cio is the concentration of interstitial oxygen in silicon,  $\chi$  is a constant  $(2<\chi<3)$ ,  $N_d-N_A$  is the free carrier concentration, and t is the time at a given temperature. Di is the diffusion constant of interstitial oxygen given by

$$D_{i} = 0.13 \times e^{\left(-\frac{E_{A}}{kT}\right)}$$

(2)

where E<sub>A</sub> is the activation energy, k is Bolzmann's constant and T is the absolute temperature. The E<sub>A</sub> value of 2.53 eV for the activation energy can be found in [10]. The model presented in (1) is based on the assumption that the TD formation kinetics is limited by the diffusion of interstitial oxygen.

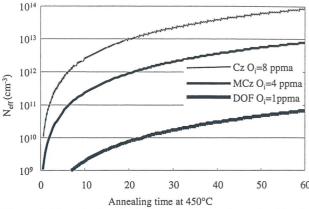

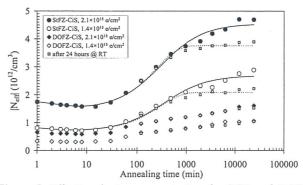

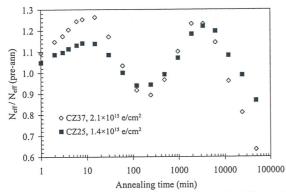

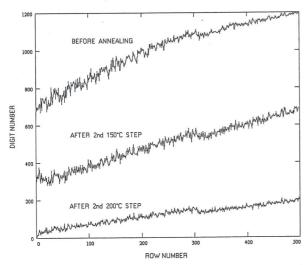

The TD generation in different oxygen rich detector materials can be roughly estimated by applying values reported in literature for the parameters in (1) and (2). Calculations were performed for standard Cz-Si (O;≈8 ppma), for Cz-Si grown with magnetic field (O<sub>i</sub>≈4 ppma) and for high-temperature long-time (HTLT) diffusion oxygenated Fz-Si (O<sub>i</sub>≈1 ppma) [11]. The effective doping concentration determined by the TD formation as a function of annealing time at 450 °C is shown in Fig.1.

Figure 1. The effective doping concentration determined by the TD formation as a function of the annealing time at  $450^{\circ}\text{C}$ . Parameter values are set to  $\chi=2.45$ ,  $a\approx2.8\times10^{-10}$  and  $b\approx5.0\times10^{-15}$ . Materials are assumed to be initially p-type, with a boron concentration of  $4.5\times10^{12}$  cm<sup>-3</sup>.

It can be seen in Fig.1 that in standard Cz-Si, where the oxygen concentration is close to the oxygen solid solubility for silicon,  $N_{eff}$  exceeds the value of  $10^{13}~\text{cm}^{-3}$  only after 20 minutes of heat treatment at 450 °C. This donor concentration would correspond to the full depletion voltage of  $\approx\!700~\text{V}$  in a 300  $\mu\text{m}$  thick detector. For the MCz-Si with lower oxygen concentration, this limit is met about after one hour. In the heavily diffusion-oxygenated material, the TD formation plays essentially no role at all. The initial doping concentration could be exceeded only after several hours of heat treatment at 450 °C, which is not the case in any practical detector fabrication processes.

## III. RADIATION HARDNESS OF CZOCHRALSKI SILICON DETECTORS

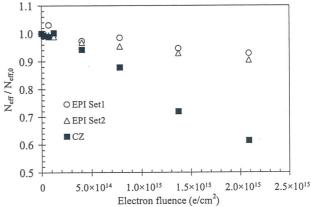

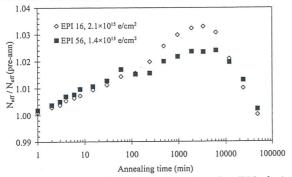

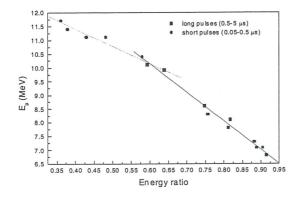

The recent availability of high resistivity Cz-Si has triggered significant amount of R&D activity. Cz-Si devices have been irradiated with various sources including low and high energy protons, neutrons,  $\gamma$ -rays, Lithium ions and electrons [12]. An example of proton irradiation results is shown in Fig.2.

As seen in Fig.2, the depletion voltage of Cz-Si is less sensitive to the increased radiation fluence than that of standard Fz-Si or DOF-Si. Even after the maximum fluence corresponding to  $5\times10^{14}$  1-MeV equivalent neutrons/cm², the depletion voltage of the Cz-Si diodes is smaller than the initial depletion voltage before irradiation, i.e. 260 V, normalized to the sample thickness of 300  $\mu$ m [13]. In Fz-Si and DOF-Si materials, the Space Charge Sign Inversion (SCSI) effect takes place after the fluence of  $\approx0.5\times10^{14}$  1-MeV equivalent neutrons/cm². On the other hand, in the Cz-Si samples the full depletion voltage seems to reach its minimum approximately at the fluence  $1.5\times10^{14}$  1-MeV equivalent neutrons/cm².

Measurements with Transient Current Technique (TCT) [14] revealed that in Cz-Si SCSI takes place at a fluence of  $\approx 2 \times 10^{14}$  1-MeV equivalent neutrons/cm<sup>2</sup>. As a comparison, a total fluence of  $1.6 \times 10^{14}$  1-MeV equivalent neutrons/cm<sup>2</sup> is predicted for the inner parts of the silicon microstrip tracker of the CMS experiment at

CERN after 10 years of operation [15]. Furthermore, the full depletion voltage in Cz-Si has not exceeded its initial value of 260 V even after the fluence of  $5\times10^{14}$  1-MeV equivalent neutrons/cm², which corresponds to more than 30 years of LHC operation. The maximum improvement in the radiation hardness of Cz-Si is achieved, however, only for the case of proton irradiations. Some improvements are also shown for neutron-irradiated detectors [16].

Figure 2. Evolution of the full depletion voltage  $(V_{depl})$  and of the effective doping concentration  $(N_{eff})$  in Cz-Si, diffusion oxygenated Fz-Si (DOF) and standard Fz-Si (FZ) irradiated with 10 MeV protons. The fluences have been rescaled to 1 MeV equivalent neutrons.

#### IV. CONCLUSIONS

It has been proved that it is possible to manufacture high quality particle detectors from high resistivity Czochralski silicon (Cz-Si). Electrical properties, i.e. full depletion voltage and leakage current, are comparable to those of traditional Float Zone silicon (Fz-Si) devices.

Many investigations in the framework of CERN RD50 Collaboration have indicated that Cz-Si is more radiation hard than standard and oxygenated Fz-Si when subjected to charge hadron irradiation. Cz-Si samples proved to be less sensitive to the depletion voltage changes as a function of irradiation particle fluence.

An interesting feature of Cz-Si is the formation of thermal donors (TD) at certain temperatures. The kinetics of TD formation depends strongly on the oxygen concentration of Cz-Si material, on the presence of hydrogen in semiconductor fabrication process and on the temperature used after the last high temperature (e.g. 1000 °C) process step, tending to suppress the TDs. When processing p<sup>+</sup>-n<sup>-</sup>-n<sup>+</sup> detectors on n-type phosphorous-doped Cz-Si substrates, the TD formation decreases the effective bulk resistivity and consequently increases the bias voltage required to fully deplete the substrate.

On the other hand, if the starting material is boron-doped p-type high-resistivity Cz-Si, the TD generation process can be utilized in order to produce p<sup>+</sup>-n<sup>-</sup>-n<sup>+</sup> detectors. The last thermal process step, i.e. the sintering of aluminium, is intentionally carried out at the temperature where TDs are created. Due to the generated donors, the p<sup>-</sup>-type bulk will eventually be compensated to n-type bulk.

With this method it is possible, with low cost and with a process of low thermal budget, to fabricate detectors with high oxygen concentration that can be depleted with bias voltages lower than 100 V. Because of the exponential dependence of the oxygen concentration on TD generation, a homogenous oxygen concentration is essentially important. The use of magnetic field during the Cz-Si crystal growth may be necessary in order to meet satisfactory homogeneity.

The radiation hardness of  $p^+$ -n (inverted)-n<sup>+</sup> detectors will be studied in the incoming RD50 irradiation campaigns.

#### V. ACKNOWLEDGEMENTS

This work has been performed in the framework of CERN RD39 and RD50 Collaborations and has partially been financed by the Academy of Finland.

<sup>[1]</sup> G. Linstroem et al., Nucl. Instr. Meth., A466 (2001) 308.

<sup>[2]</sup> Z. Li et al., IEEE Trans. Nucl. Sci., 39 (1992) 1730.

<sup>[3]</sup> V. Savolainen et al., J. Crystal. Growth, 243 (2002) 243.

<sup>[4]</sup> J. Härkönen et al., Nucl. Instr. Meth., A485 (2002) 159.

<sup>[5]</sup> G. S. Oehrlein, J. Appl. Phys., 54 (1983) 5453.

<sup>[6]</sup> K. Wada, Phys. Rev. B, 10 (1984) 5884.

<sup>[7]</sup> A. Ourmazd et al., J. Appl. Phys., 58 (1984) 1670.

<sup>[8]</sup> V. Emtsev et al., Appl. Phys. Lett., 68 (1996) 2375.

<sup>[9]</sup> A. Simoen et al., Appl. Phys. Lett., 81 (2002) 1842.

<sup>[10]</sup> W. Wijaranakula, Appl. Phys. Lett., 59 (1991) 1608.

<sup>[11]</sup>E. Fretwurst, "Survey of radiation damage studies at Hamburg", 3rd RD50 Workshop on Radiation Hard Semiconductor Devices for Very High Luminosity Colliders, CERN, 3-5 November 2003. On line available: http://www.cern.ch/rd50.

<sup>[12] &</sup>quot;RD50 Status Report", CERN/LHCC-2003-058 (2003) 30.

<sup>[13]</sup> E. Tuominen et al., IEEE Trans. Nucl. Sci., 50 (2003) 1942.

<sup>[14]</sup> V. Eremin et al., Nucl. Instr. Meth., A372 (1996) 188.

<sup>[15] &</sup>quot;CMS Technical proposal", CERN/LHCC 94-38 (1994).

<sup>[16]</sup>Z. Li et al., "Radiation hardness of high resistivity CZ Si detectors after gamma, neutron and proton radiations", accepted for publication in IEEE Trans. Nucl. Sci.

## Development of a fabrication technology for PIN diodes on thinned silicon substrate

S. Ronchin<sup>1</sup>, M. Boscardin<sup>1</sup>, G.-F. Dalla Betta<sup>2</sup>, P. Gregori<sup>1</sup>, V. Guarnieri<sup>1</sup>, C. Piemonte<sup>1</sup>, N. Zorzi<sup>1</sup>

<sup>1</sup>ITC-irst, Divisione Microsistemi, Via Sommarive 18, Povo (Trento), I-38050, Italy

<sup>2</sup>Dipartimento di Informatica e Telecomunicazioni, Università di Trento, Povo (Trento), I-38050, Italy

#### I. INTRODUCTION

In the last ten years, an extensive research activity in the field of silicon radiation detectors has been strongly focused on the strict requirements of the future CERN-LHC (Large Hadron Collider). The detectors, to be used for these experiments, will be exposed to very high fluences of particles in the 10 years of operation, with a foreseen luminosity of about 10<sup>34</sup> cm<sup>-2</sup>×s<sup>-1</sup>, resulting in a consequent performance degradation. Radiation damage induces several detrimental effects on high resistivity silicon detectors [1],[2], among them, the growth of the full depletion voltage after substrate type inversion is of particular concern. The usage of very thin detectors is one possible strategy in order to face this problem. The direct advantage of such approach is the reduced depletion voltage even after high irradiation fluences. Moreover, the starting resistivity of a thin sensor can be much lower than standard devices with 300 µm thickness, preserving a low depletion voltage (100-200 V) and, as a consequence, the type inversion can be delayed to higher irradiation fluences. Finally, an improvement of the tracking precision and momentum resolution is expected.

Thin diode detectors have been already employed in many applications such as  $\Delta E$ -E telescopes for heavy ion detection and tracking [3]-[5], short range particle detection under high  $\gamma$ -ray background [4], X-ray (E>10 keV) beam monitoring [4], and in all the applications where high radiation selectivity, short particle path and reduced multiple scattering of charged particles are required [3]-[6].

Very thin silicon wafers ( $< 200 \, \mu m$ ) cannot be easily handled by the standard equipment used in fabrication lines. Thus, a mechanical lapping cannot be used to thin the wafers down to the required depth ( $50\text{-}100 \, \mu m$ ). The most convenient approach is a local thinning adopting the technology used for micro-machined sensors, based on dry or wet etching. Several techniques are available [7], among them the wet anisotropic silicon etchant TMAH (Tetra-Methyl Ammonium Hydroxide) has recently gained considerable interest because of the CMOS process compatibility. Furthermore, the TMAH shows a very good etching uniformity and a relatively high selectivity for silicon with respect to oxides and nitrides at some fixed TMAH weight-% (wt%) concentrations [8].

The aim of this work is to show the feasibility of thin detectors satisfying the requirements for the new generation detectors. In particular, we report on the

development of a fabrication technology for the realization of PIN diodes on membranes obtained by locally thinning the silicon substrate by means of TMAH etching from the wafer backside. Diodes of different shapes and sizes have been fabricated on 50  $\mu m$  and 100  $\mu m$  thick membranes. They have been tested, showing a low leakage current ( $\approx\!2$  nA/cm² for the 50  $\mu m$  membrane) and, as expected, a very low depletion voltage ( $\approx\!1$  V).

#### II. FABRICATION PROCESS

The fabrication process of a detector on a thin silicon membrane is based on a pre-existent technology developed at ITC-irst for PIN diodes, adding the etching step of the wafer backside. In particular, the silicon etching is performed using a solution with a concentration of 25 wt% of TMAH at a temperature of 90 °C.

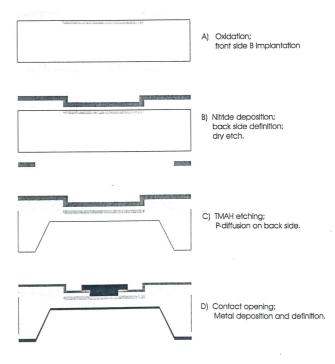

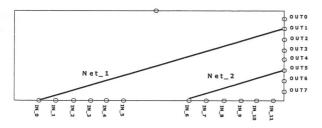

Fig.1 shows the schematic flowchart of the fabrication process that requires 5 mask steps: 4 on the front side and one to define the membranes on the backside.

Figure 1. Schematic process flow for the fabrication of a thin diode on n-type substrate.

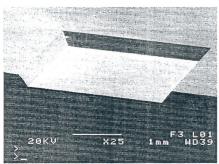

The main characteristics of the silicon wafers for device processing are: 100 mm diameter, Floating Zone (FZ), 300  $\mu m$  thick, <100> oriented, phosphorus doped with 6 k0xcm nominal resistivity. We have etched two groups of wafers for different times obtaining two different silicon membrane thickness of  $\approx\!\!50~\mu m$  and  $\approx\!\!100~\mu m$ , respectively, as reported in Table I: the wafer thickness was measured by a micrometer and the etching depth by a microscope comparator. Fig.2 shows, as an example, the SEM photograph of the cross section for a thinned region.

It is worthwhile to note that on the wafers treated with TMAH there are also some devices that have not been etched. In addition, two wafers are processed without the TMAH etching as a reference for the electrical characterization.

TABLE I. TMAH-ETCHED WAFERS.

| Wafer  | Wafer thickness | Etching depth | Membrane  |

|--------|-----------------|---------------|-----------|

| number | (µm)            | (µm)          | thickness |

|        |                 |               | (µm)      |

| 3      | 296±2           | 191±2         | 105±3     |

| 4      | 298±7           | 199±1         | 99±7      |

| 5      | 295±1           | 196±2         | 99±2      |

| 6      | 296±8           | 239±2         | 57±8      |

| 7      | 302±3           | 245±3         | 57±4      |

| 8      | 300±3           | 201±1         | 99±3      |

| 9      | 306±6           | 257±2         | 49±6      |

Figure 2. SEM photograph of a cross section for a silicon membrane obtained with TMAH etching. The white line indicates 1 mm.

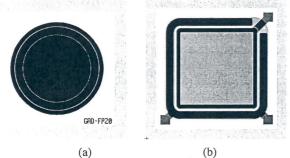

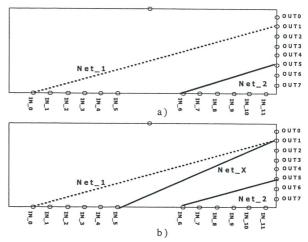

Figure 3. Layout of two different types of produced diodes: a) round diode with area of 2.27 mm<sup>2</sup> and double guard-ring (FP20); b) square diodes of various areas: 0.75, 1.9, 3.5, 11.35 and 19.1 mm<sup>2</sup> with single guard-ring.

#### III. DEVICE DESCRIPTION

We adopted in this process a wafer layout previously employed to the production of PIN diodes with different

active areas and shapes (see an example in Fig.3). A new mask has been added for the definition of the backside areas to be thinned. Being the etching angle for <100> silicon of 54.74°, one has to carefully oversize the holes in order to fabricate the device entirely inside the thinned region. In order to monitor the main parameters characterizing the fabrication technology, a set of standard test structures (diodes, MOS capacitors, gated diodes) is included.

#### IV. ELECTRICAL CHARACTERIZATION

#### IV.A. Technological Parameters

First, we compared the parameters extracted from 300  $\mu m$  thick test structures from wafers processed with and without TMAH etching step, in order to evaluate the effects of the TMAH etchant on the electrical characteristics. The results, grouped by reference and TMAH-treated wafers, are summarized in Table II. Since no significant differences are observed in the values obtained for the two groups of wafers, we conclude that the TMAH treatment does not induce any damaging effect on the electrical parameters of the devices.

Table II. Comparison of the main electrical parameters measured on 300  $\mu m$  thick test structures on wafers processed with and without TMAH etching.  $V_{FD}, N_D, J$  and  $\tau_g$  are extracted from test diodes.  $T_{ox}, Q_{ox}, V_{FB}$  are obtained from MOS capacitors with the isolation oxide as dielectric.  $s_0$  is evaluated on gate controlled diodes.

|                                                                           | Reference | TMAH-treated |

|---------------------------------------------------------------------------|-----------|--------------|

| Full depletion voltage V <sub>FD</sub> (V)                                | 17.6      | 13.5         |

| Doping concentration N <sub>D</sub> (10 <sup>11</sup> cm <sup>-3</sup> )  | 2.6       | 2.0          |

| Leakage current density J (nA/cm²)                                        | 2.7       | 2.2          |

| Carrier generation lifetime τ <sub>g</sub> (ms)                           | 18        | 22           |

| Oxide thickness Tox (nm)                                                  | 438       | 437          |

| Oxide charge density Q <sub>ox</sub> (10 <sup>10</sup> cm <sup>-2</sup> ) | 1.4       | 1.4          |

| Flatband voltage V <sub>FB</sub> (V)                                      | 0.77      | 0.77         |

| Surface generation velocity s <sub>0</sub> (cm/s)                         | 2.5       | 3.0          |

#### IV.B. Characteristics of the Thinned Diodes

TMAH-etched wafers have been electrically characterized by capacitance-voltage (C-V) and current-voltage (I-V) measurements on devices manufactured both on the thinned membranes and on the full thickness bulk.

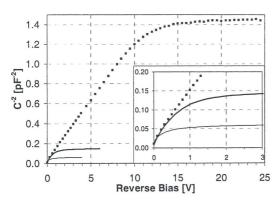

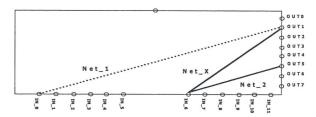

As an example, the  $1/C^2$ -V characteristics for 300  $\mu$ m, 100  $\mu$ m and 50  $\mu$ m thick FP20 diodes are reported in Fig.4. The full depletion voltage of these devices is 13 V, 1 V and lower than 1 V, respectively.

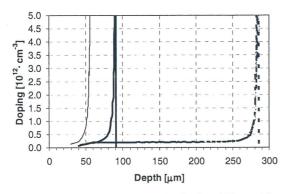

Fig.5 exhibits the doping profiles, extracted by C-V measurements performed on FP20 diodes: the calculated thicknesses are very close to the previously measured data reported in Table I for the wafer numbers 4 and 6.

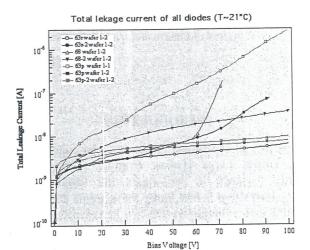

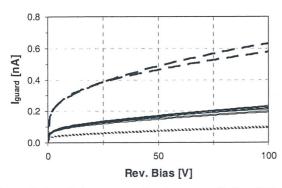

Fig.6 shows the guard-ring currents of several thinned devices having different thicknesses. These data refer to diodes having an area of 1.9 mm<sup>2</sup>. As expected, the guard-ring currents are very similar for all devices having the same thickness. It is worthwhile to note that the guard-ring current does not show any breakdown within a bias voltage of 100 V.

Figure 4.  $1/C^2$ -V characteristics for FP20 diodes: 300  $\mu$ m (dotted lines), 100  $\mu$ m (thick line) and 50  $\mu$ m (thin line) thick devices. The inset shows a magnification at low voltages.

Figure 5. Doping profiles for FP20 diodes: 300  $\mu$ m (dotted lines), 99  $\mu$ m (thick line) and 50  $\mu$ m (thin line) thick devices.

Figure 6. Guard-ring currents for the square diodes of 1.9 mm<sup>2</sup> area: 300  $\mu$ m (dashed lines), 100  $\mu$ m (continuous lines) and 50  $\mu$ m (dotted lines) thick diodes.

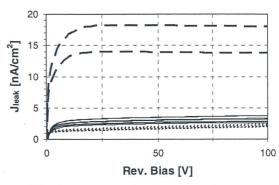

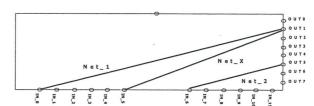

In Fig.7 a comparison between the diode current densities of thin and non-thinned devices is shown. The diodes show a low leakage current density at 100 V of  $\approx 3$  nA/cm² for 100  $\mu m$  and 2.1 nA/cm² for 50  $\mu m$  thick devices. These values are much lower than the ones reported in [4],[5],[9],[10], and comparable to that reported in [3], where the devices are obtained using a similar process.

The average leakage current at 100 V and the average full depletion voltage, measured on square PIN diodes of  $1.9 \text{ mm}^2$  area, are reported in Table III. It is interesting to observe that the values for the etched devices are lower than expected. Indeed, as the generation volumes of the etched devices are about 1/3 and 1/6 of the  $300 \mu \text{m}$  thick ones, also the currents should respect these ratios.

Instead, in our cases, ratios of about 1/5 and 1/8 are observed, respectively. A possible explanation can be a more efficient gettering of impurities for thin membranes.

Nevertheless, the thinned diodes show a leakage current weakly dependent on the thickness. It may be ascribed to the fact that the bulk component of the current is so small that the surface contribution becomes dominant. This is appreciable also from the marked slope of the current after full depletion.

Figure 7. Leakage current density measured on square PIN diodes of 1.9 mm<sup>2</sup> area: 300  $\mu$ m (dashed lines), 100  $\mu$ m (continuous lines) and 50  $\mu$ m (dotted lines) thick diodes.

Table III. Summary of the electrical characterization of the square PIN diodes with 1.9  $\mathrm{mm}^2$  area.

| Device thickness (µm) | Leakage current at 100 V (nA/cm <sup>2</sup> ) | Full depletion voltage (V) |

|-----------------------|------------------------------------------------|----------------------------|

| 300                   | 16±1                                           | 22                         |

| 100                   | 3.0±0.4                                        | 2.2                        |

| 50                    | 2.1±0.2                                        | 1.2                        |

#### V. CONCLUSIONS

TMAH-etching is a suitable technique for producing thin PIN diode detectors. We have produced samples on  ${\approx}50~\mu m$  thick membranes having a full depletion voltage of  ${\approx}1~V$  and a leakage current close to 2 nA/cm² at 100 V. Moreover, no breakdown up to 100 V is noticed and no differences in the technological parameters of TMAH-treated wafers with respect to wafers processed without silicon etching are observed.

Radiation damage characterization on samples irradiated with 58 MeV Li ions and charge collection efficiency measurements are in progress.

- [1] M. Moll, Nucl. Instr. Meth., A511 (2003) 97.

- [2] M. Bruzzi, IEEE Trans. Nucl. Sci., 48 (2001) 960.

- [3] L. Evensen et al., IEEE Trans. Nucl. Sci., 44 (1997) 629.

- [4] F. Foulon et al., IEEE Trans. Nucl. Sci., 46 (1999) 218.

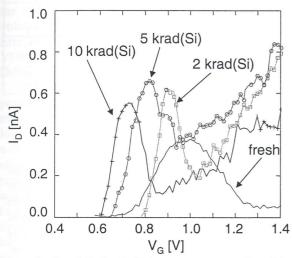

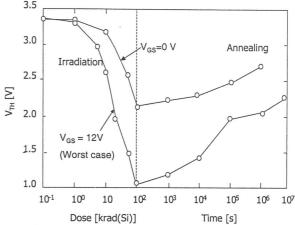

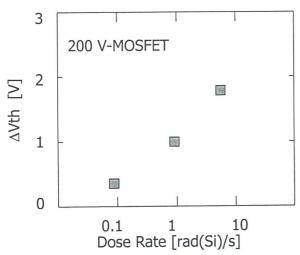

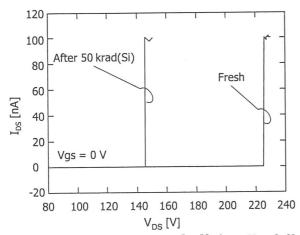

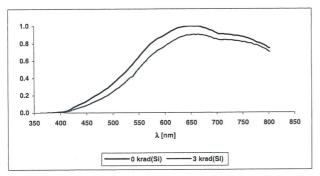

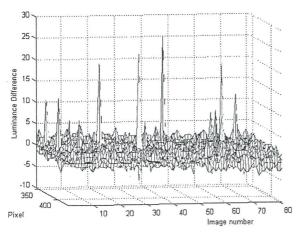

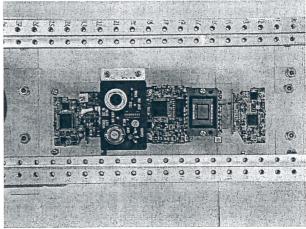

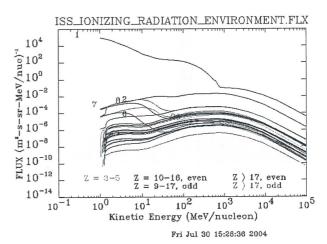

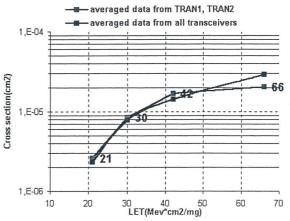

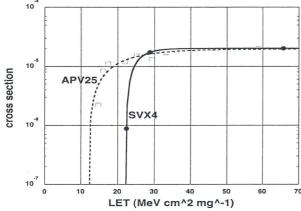

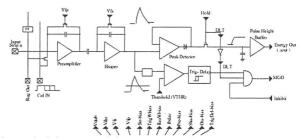

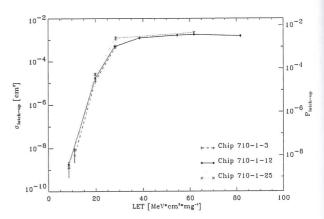

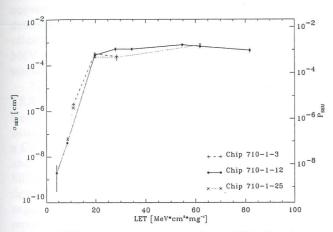

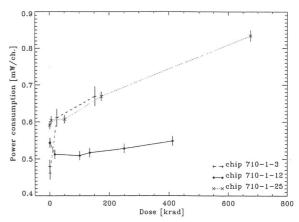

- [5] L. Stab, Nucl. Instr. Meth., A288 (1990) 24.[6] R. Horisberger, Nucl. Instr. Meth., A288 (1990) 87.