Content Addressable Memory (CAM) cells developed to be integrated into chips that can be used to solve pattern recognition problems, such as DNA sequence analysis or image recognition.

How does it work?

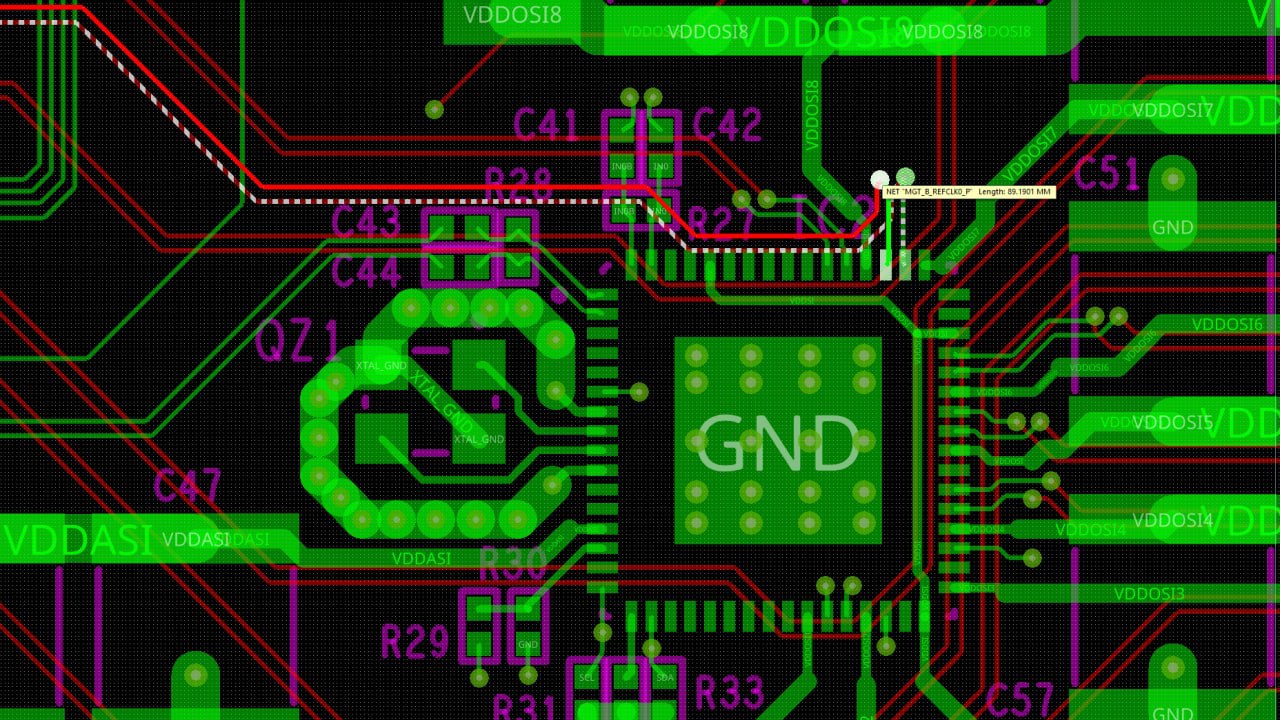

The CAM memory architecture is designed to reduce the length of the data lines and consequently reduce the energy consumption linked with the propagation of data over the lines. In addition, a matching circuit enables the reduction of the consumption linked with the search phase, ensuring an optimization in the comparison between the data present and the data entered. If one of the bits of the entered word does not find a match, the cell sends a kill signal that inhibits the switching of downstream cells. Thanks to this feature, the cell matrix requires less than 0.4 fJ/bit for comparison in HPC (High Power Computing) technologies and less than 0.2 fJ/bit for HPL (High Power Low-leakage) technologies. The CAM cell was designed in two variants, in 28 nm CMOS technology using a fully-CMOS approach. A prototype containing these cells was manufactured and tested, up to 400 MHz, confirming the expected performance.

Applications

- Image recognition;

- Identification of genetic sequences;

- analysis of images or biomedical data.

Advantages

- Speeding up of processes for pattern recognition problem solving;

- With the same computing power, reduced energy consumption compared to FPGA and GPU;

- It can be easily integrated as an IP-block in an ASIC.

ADDITIONAL DETAILS

PATENT OWNERS

INFN

PRIORITY NUMBER

IT 102016000077445

TECHNOLOGY SECTOR

Electronic circuits

TT CODE

P_15.016

CONTACT US

For more information about this technology, WRITE TO US